可重构计算结构采用一种将指令流驱动处理器的功能灵活性和数据流驱动处理器的高能效结合在一起的计算方式,在性能、功耗和功能灵活性等芯片的关键指标之间具有更好的平衡,成为应对硬件专用化和应用灵活性需求的一种必然的选择。人工智能、计算机视觉和视频处理等应用兼具计算密集与访存密集的性能需求,对处理器芯片的计算能力和灵活性同时提出挑战,可重构阵列处理器基于软件框架而非某些应用领域计算特征进行硬件的功能定义,能够较好的平衡计算效能和支持算法演进的功能灵活性需求。

现有的可重构体系结构集高性能、高灵活性、 高并行性和低功耗、低成本等优点于一身,但是无论是细粒度的FPGA(Field-Programmable Gate Array)还是粗粒度的CGRA(Coarse-Grained Reconfigurable Arrays)多多少少存在重构开销大、编程复杂度高等缺点。为此,项目致力于探索效能驱动、以软件编程实现处理器功能的动态实时自重构的创新体系结构,解决“通信墙”、“存储墙”和“编程墙”问题,弥合硬件专用化和应用灵活性鸿沟。

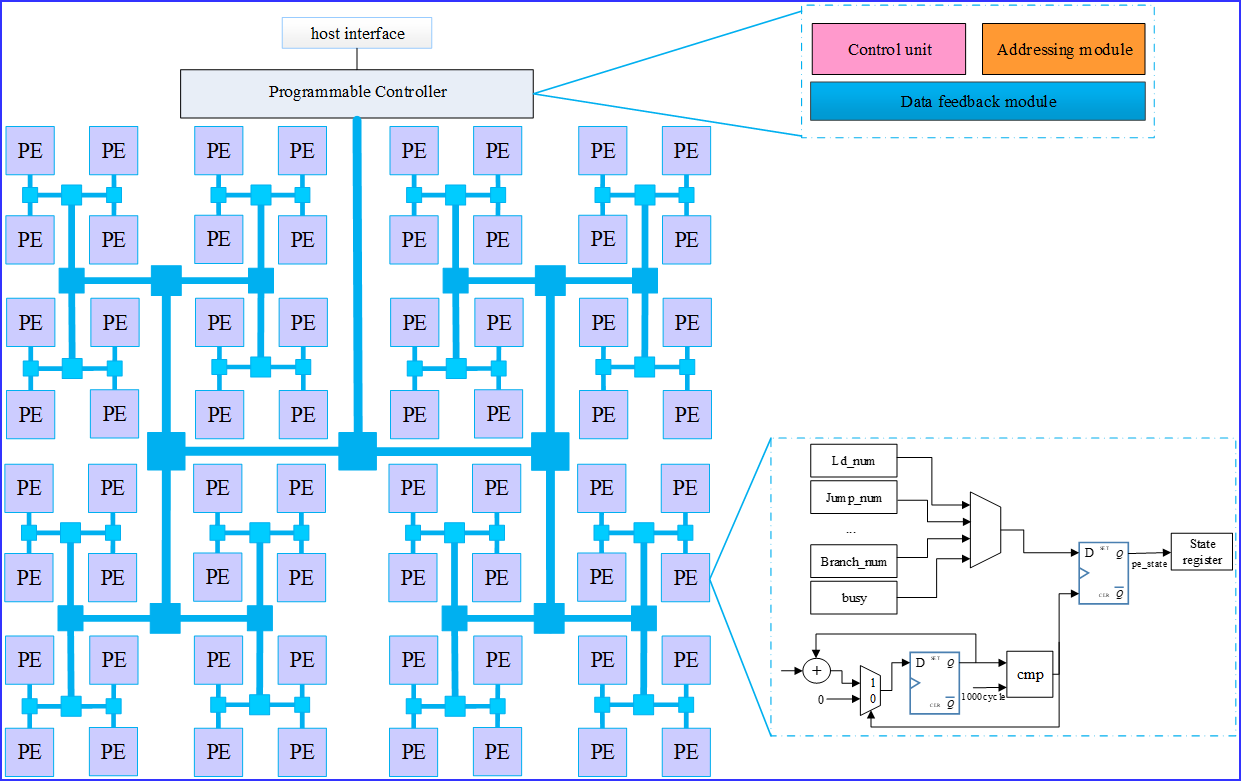

首先,为了降低重构时延,提高计算效率,提出了一种指令流和数据流双模混合驱动、负载均衡的动态自重构机制。如图1所示。PE灵活的工作模式满足了应用的不同计算需求,从而达到提高计算效率的目的。PE功能的重构不需要主控CPU的参与,而是利用PE间的邻接互连短线和层次化的H树配置网络完成配置信息的下发、回收,实现可编程控制器对执行状态的实时监测、控制和功能配置,实现阵列处理器的动态自主重构。大大降低了重构的开销。

图1 动态可编程自重构体系结构APR

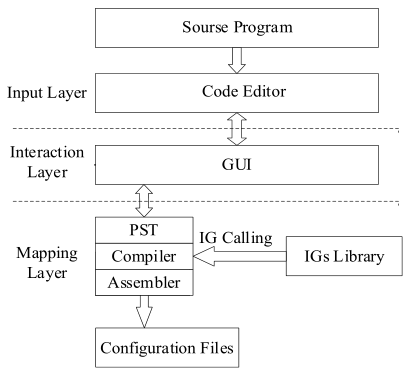

其次,基于所提处理器灵活的自重构结构设计了设计一种基于程序切片和翻译的软件栈,如图2所示。在前端利用后向静态切片将复杂的高级语言(High-Level Languages,HLLs)程序解构为操作类型固定且结构简单的元片,以凸显抽象操作的时空特征。在底层将HLLs共有操作的机器码序列封装成指组(Instruction Groups,IGs),以提升硬件描述的语义抽象层次,将硬件相关物理细节与中间表示剥离,提高了编译器的可移植性。依据已实现的算法数据流图及其不同优化目标下的配置信息构建常用算法模板库,在映射过程中直接调用模板库,实现了高级语言到可重构结构的自动化编译优化和映射。支撑了重构处理器的可编程功能。

图2 面向自重构处理器的软件栈

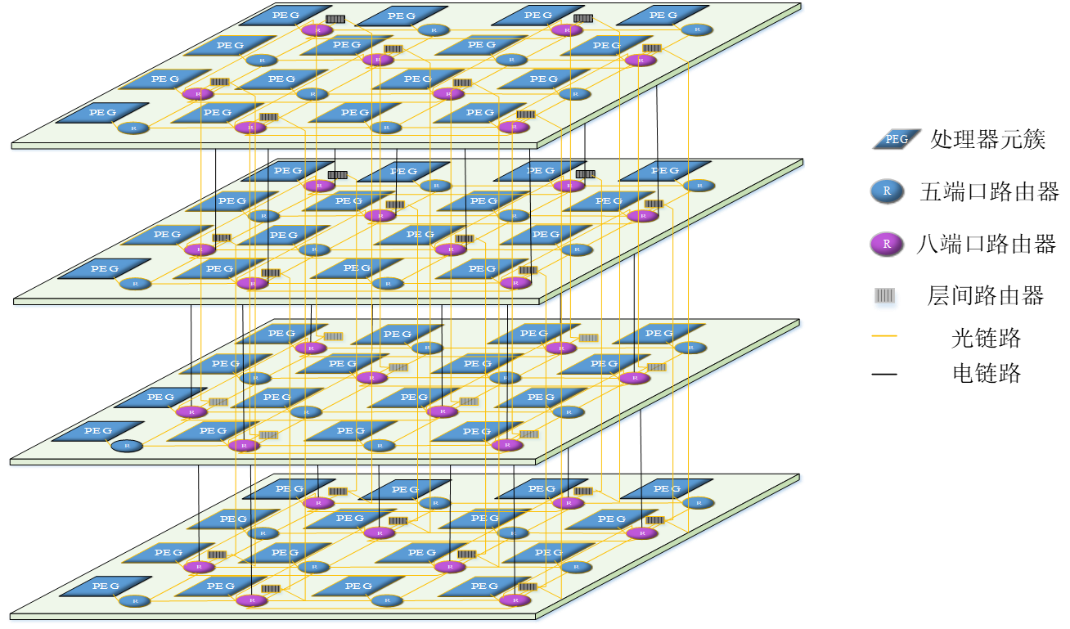

然后,为了减少阵列处理器的层内节点通信路径距离、提高整体通信带宽,充分考虑光互连和电互连以及硅通孔(Through Silicon Vias,TSV)的优势,基于Mesh结构和Tours结构建立三维光电混合互连网络结构,如图3所示。设计了一种避免反向阻塞的层内自适应路由算法和优先跨簇的层间自适应路由算法,以及对应的自适应光电混合路由器,可根据流量特征在光链路传输和电链路传输间自动切换。

图3 基于Mesh和Tours的多层三维互连(3D-AOHI)结构

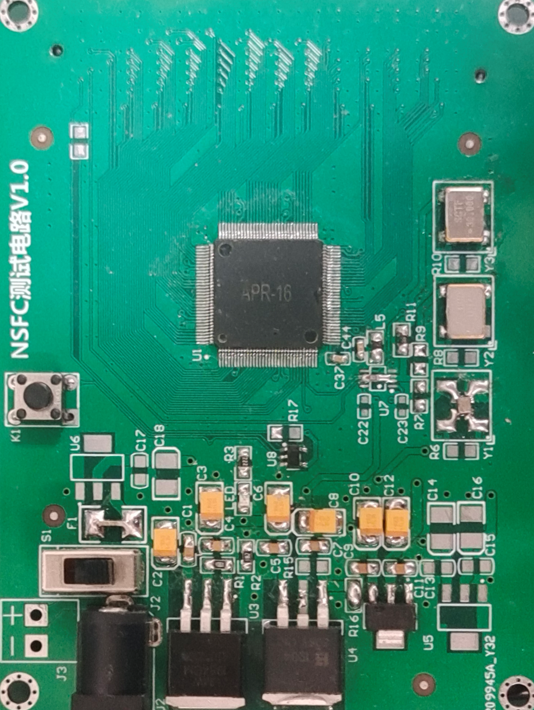

为了验证所提可编程自重构体系结构APR的可扩展性及其支持大规模PE阵列的能力,基于XCVU440-1FLGA2892C FPGA开发了APR-1024原型系统,并完成了16个PE的APR-16芯片设计及SMIC 55nm CMOS工艺的流片。基于APR-16,实现了DCGAN的映射及功能、性能测试。基于APR-1024原型系统对HEVC中帧内环路和帧间环路进行了应用开发及功能、性能测试。基于APR架构的嵌入式车载仪表显示芯片已在西安恩狄集成电路有限公司实现产业化,产生了一定的经济效益。

图4 APR-16芯片测试板